使用して評価する中で温度安定度や電源投入時の変動による使いづらい点を変更することにしました。

またMCカートリッジ使用の場合ゲインが足らないので初段にFETを入れてゲインを稼ぐことにしました。

また直流電流を流せないトランスを使用しているので無理せずコンデンサカットすることにしました。

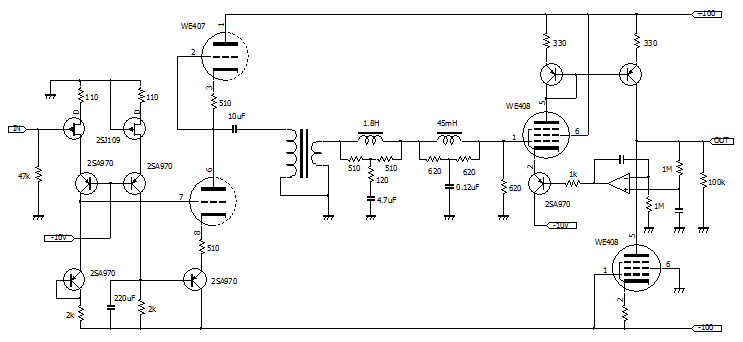

ラインアンプもWE407(プレート-カソード電圧が150V以上必要)を使用するため回路が複雑になっていましたがWE408を使うことによりシンプルに変更しました。 |

| |

2019/3/1 |

|

|

|

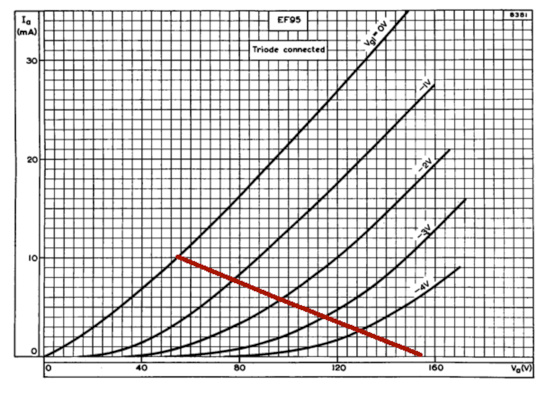

WE408とヒーター電圧が違うだけの真空管の中からEF95のデーターシートに三極管特性が載っていましたので設計の参考にしました。

下がそのグラフで負荷線を引いてみました。

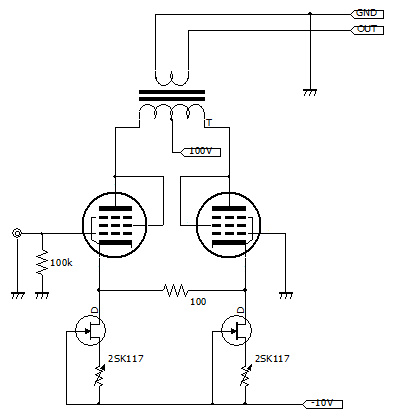

電源100Vでプレート電流を5~6mA流しても十分な振幅が得られることでシンプルな回路になりました。左の回路のままでは差動動作とならないためトランスの二次側から帰還をかけて使います。

2SK117は6mA前後でIqポイントのFETなので選びました。GRランクの中から6mA前後のものを選び採用しました。カソード側の抵抗をなくすことによりグランド動作も可能となるかもしれません。(Vds=2V) |

| |

|

|

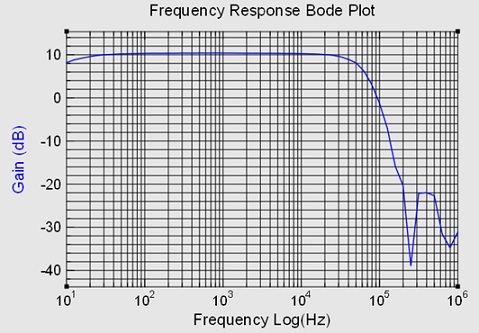

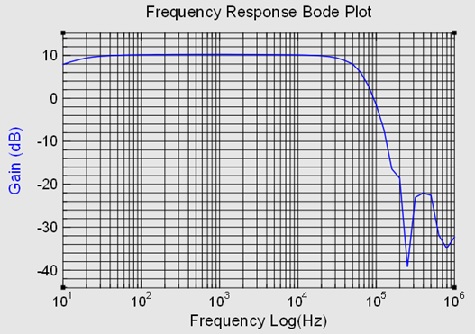

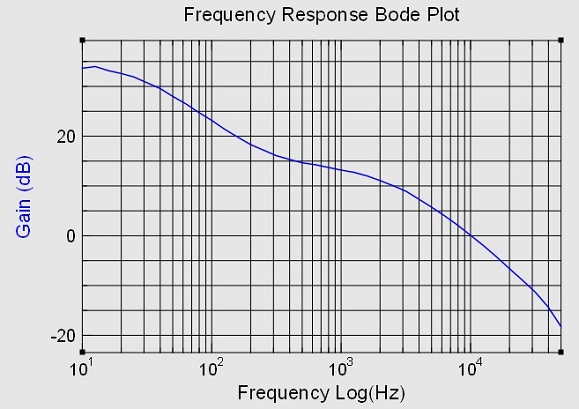

| 820Ω負荷時の周波数特性を下に載せておきます。無負荷では17dBほどありますが80kHzあたりにピークが出ます。カソード側の定電流はグランドで動かしています。 |

| |

2023/5/5 up |

|

|

|

|

|

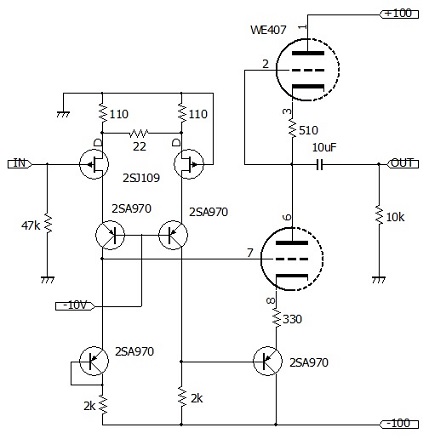

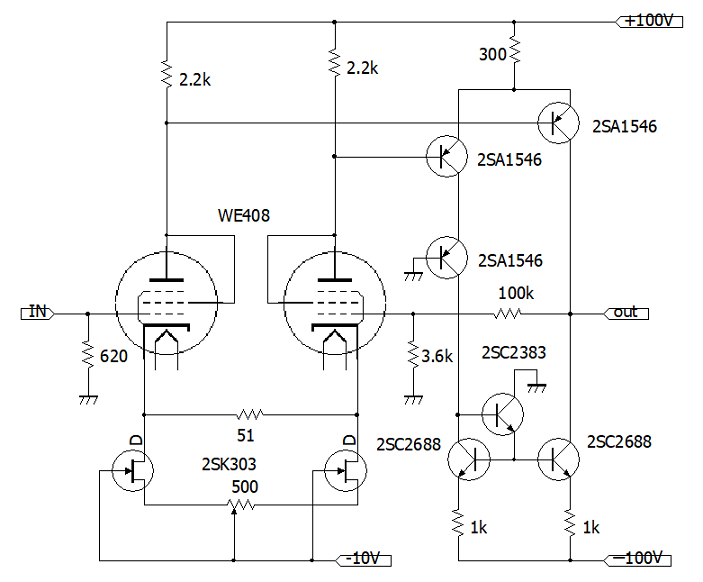

初段はPチャンネルのJFETを使用します。FETは耐圧が低いのでPNPトランジスタをカスコード接続しました。

FETの温特を補正するために同様の定電流回路を使用して2段目のバイアス電圧を作り出しています。2段目はWE408を三極管接続させSRPP構成にしています。

中点電圧は真空管のバラツキによりますがほぼ数ボルトのプラス電圧になります。

このためトランスとの間にカップリングコンデンサを投入します。

|

| |

2019/3/1 |

| ラインアンプでは、電源100VでWE407の使用ができなくなりましたが、イコライザ回路では3mA動作なので使えそうです。 |

| |

2019/3/6 |

|

|

|

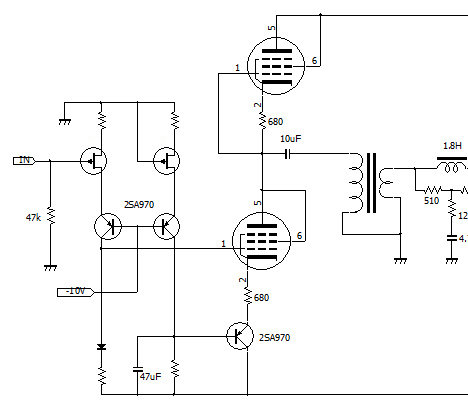

最終予定回路を掲載しておきます。初段のFETに2ch入りの2SJ109BLを使用し2mA程度の電流を流します。定電流動作で2段目のグリッドとカソードにDCバイアスをあたえます。これにより温度でGK電圧が変動しないように動きます。真空管の電流を3mAほどに押さえたのでWE407でも100V弱で動作可能としています。

右の写真が初段部分のブロックでケースの中にFETやトランジスタの付く基板が入っています。

初段アンプとLCRまでの周波数特性が下のグラフです。 |

|

2023/5/9 up |

|

|

|

トータルゲインをもう少し上げる事と片側をバイアスだけに使用するのはもったいないので差動動作としました。

本来+10Vもあるので定電流の差動を組むこともできるのですが、今回は組んだ基板の改良を行うので左の回路にしています。

右の真空管の下側のカソード抵抗はプレート電圧が丁度バランスするように抵抗値を変更しています。

この変更により歪も改善されています。 |

| |

2023/5/9 up |

|

|

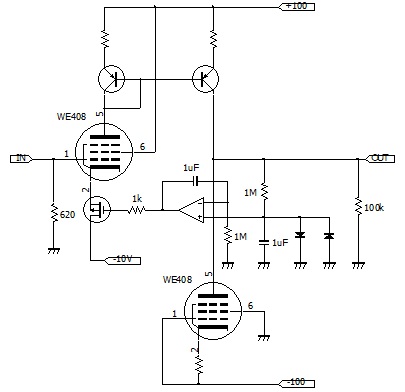

2段目のアンプも電源投入時の真空管のアンバランスな起動を考え保護ダイオードとDC帰還部のトランジスタをバイポーラからMOSへ変更してみました。Vbeの逆耐圧が6Vなので耐圧が±20V のMOSへ変えて見ました。回路的には逆耐圧を超えるような動きはしないはずですが念のため。

オペアンプの入力に付けたダイオードは、真空管の起動時の動作アンバランスや1つだけ真空管が壊れた場合の保護として必要になります。 |

| |

2019/6/2 |

|

| 回路をオペアンプを使用しない回路構成に変更してみました。上の回路は、1段アンプですが2段構成にして帰還量を増やすことにより安定なDCアンプが構成できます。位相補償は必要です。 |

| |

|

|

|

| |

|